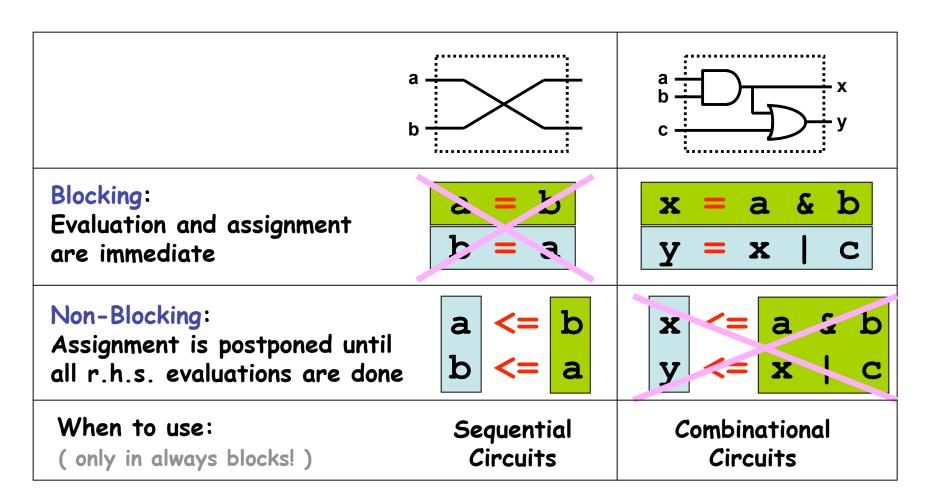

### I. Blocking vs. Nonblocking Assignments

- Verilog supports two types of assignments within always blocks, with subtly different behaviors.

- · Blocking assignment: evaluation and assignment are immediate

Nonblocking assignment: all assignments deferred until all right-hand sides have been evaluated (end of simulation timestep)

Sometimes, as above, both produce the same result.

Sometimes, not!

# Why two ways of assigning values?

Conceptual need for two kinds of assignment (in always blocks):

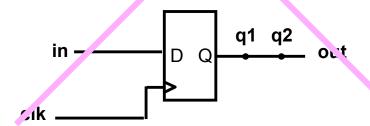

#### Assignment Styles for Sequential Logic

Will nonblocking and blocking assignments both produce the desired result?

```

module nonblocking(in, clk, out);

module blocking(in, clk, out);

input in, clk;

input in, clk;

output out;

output out;

reg q1, q2, out;

req q1, q2, out;

always @ (posedge clk)

always @ (posedge clk)

begin

begin

q1 <= in;

q1 = in;

q2 \leq q1;

q2 = q1;

out <= q2;

out = q2;

end

end

endmodule

endmodule

```

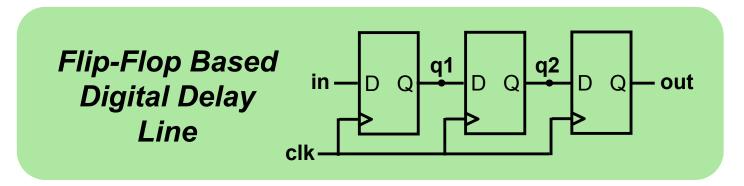

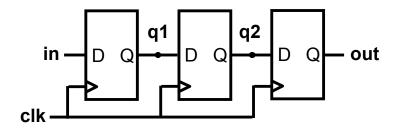

### Use Nonblocking for Sequential Logic

```

always @ (posedge clk)

begin

q1 <= in;

q2 <= q1;

out <= q2;

end</pre>

```

"At each rising clock edge, *q1*, *q2*, and out simultaneously receive the old values of *in*, *q1*, and *q2*."

"At each rising cluck edge, q1 = in.

After that, q2 = qi = in; After that,

out = q2 = r, t = in; Finally out = in."

- Blocking assignments do not reflect the intrinsic behavior of multi-stage sequential logic

- Guideline: use <u>nonblocking</u> assignments for <u>sequential</u> always blocks

### Use Blocking for Combinational Logic

| Blocking Behavior                                           | abc x y |  |  |

|-------------------------------------------------------------|---------|--|--|

| (Given) Initial Condition                                   | 11011   |  |  |

| <ul><li>a changes;</li><li>always block triggered</li></ul> | 01011   |  |  |

| x = a & b;                                                  | 01001   |  |  |

| y = x   c;                                                  | 01000   |  |  |

```

always @ (a or b or c)

begin

x = a & b;

y = x | c;

end

```

| No | ablocking Behavior                                          | abc x y | Deferred        |

|----|-------------------------------------------------------------|---------|-----------------|

|    | (Given) Initial Condition                                   | 11011   |                 |

|    | <ul><li>a changes;</li><li>always block triggered</li></ul> | 01011   |                 |

|    | x <= a & b;                                                 | 01011   | <b>~&lt;=</b> 0 |

|    | y <= x   c;                                                 | 01011   | x<=0, y<=1      |

|    | Assignment completion                                       | 01001   |                 |

- Nonblocking assignments do not reflect the intrinsic behavior of multi-stage combinational logic

- While nonblocking assignments can be hacked to simulate correctly (expand the sensitivity list), it's not elegant

- Guideline: use <u>blocking</u> assignments for <u>combinational</u> always blocks

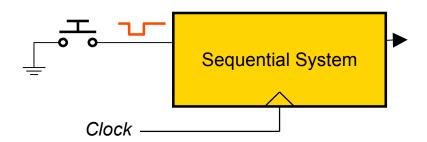

### II. Single-clock Synchronous Circuits

We'll use Flip Flops and Registers – groups of FFs sharing a clock input – in a highly constrained way to build digital systems.

#### Single-clock Synchronous Discipline:

- No combinational cycles

- Single clock signal shared among all clocked devices

- Only care about value of combinational circuits just before rising edge of clock

- Period greater than every combinational delay

- Change saved state after noiseinducing logic transitions have stopped!

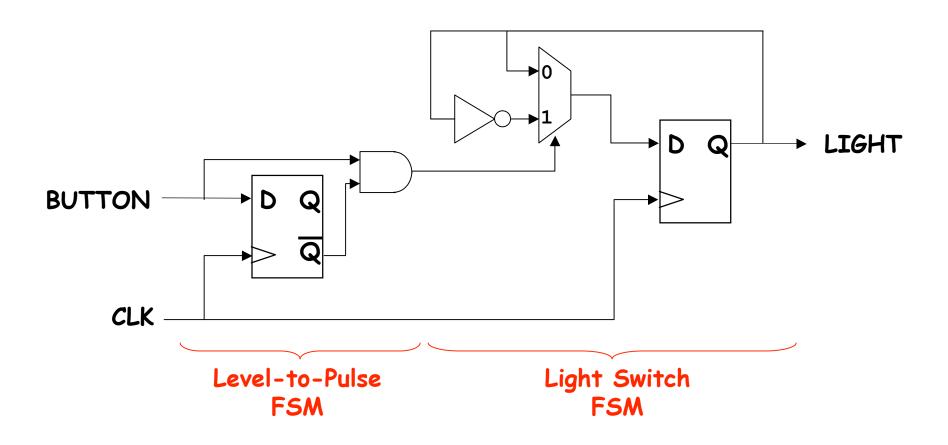

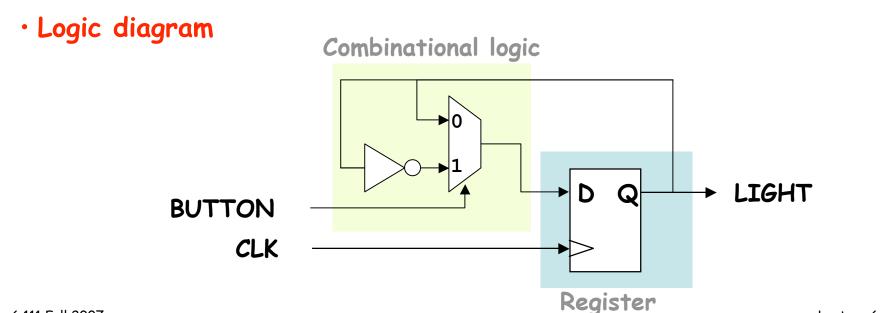

#### Clocked circuit for on/off button

```

module onoff(clk,button,light);

input clk,button;

Does this work

output light;

with a 1Mhz

reg light;

CLK?

always @ (posedge clk)

begin

if (button) light <= ~light;</pre>

end

endmodule

D

LIGHT

LE

BUTTON

CLK

CLK

LOAD-ENABLED REGISTER

SINGLE GLOBAL CLOCK

```

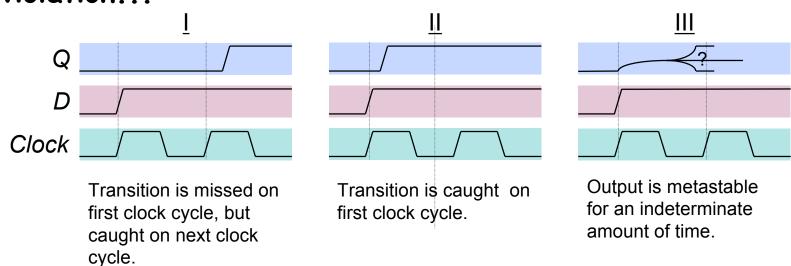

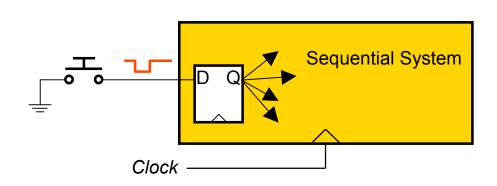

#### Asynchronous Inputs in Sequential Systems

#### What about external signals?

Can't guarantee setup and hold times will be met!

# When an asynchronous signal causes a setup/hold violation...

Q: Which cases are problematic?

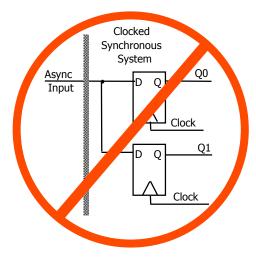

#### Asynchronous Inputs in Sequential Systems

All of them can be, if more than one happens simultaneously within the same circuit.

Idea: ensure that external signals directly feed exactly one flip-flop

This prevents the possibility of I and II occurring in different places in the circuit, but what about metastability?

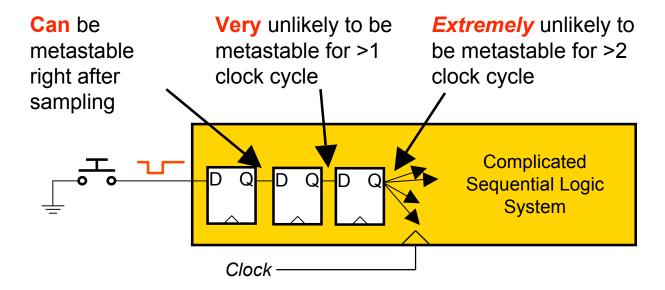

# Handling Metastability

- Preventing metastability turns out to be an impossible problem

- High gain of digital devices makes it likely that metastable conditions will resolve themselves quickly

- · Solution to metastability: allow time for signals to stabilize

#### How many registers are necessary?

- Depends on many design parameters(clock speed, device speeds, ...)

- In 6.111, a pair of synchronization registers is sufficient

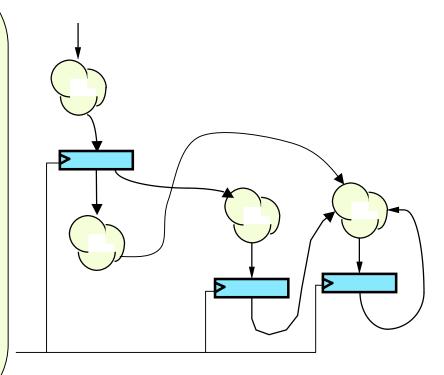

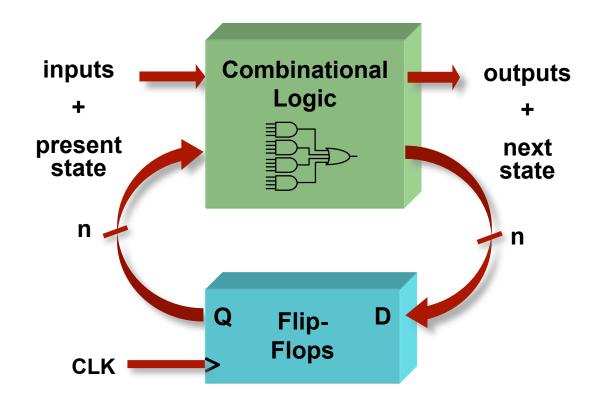

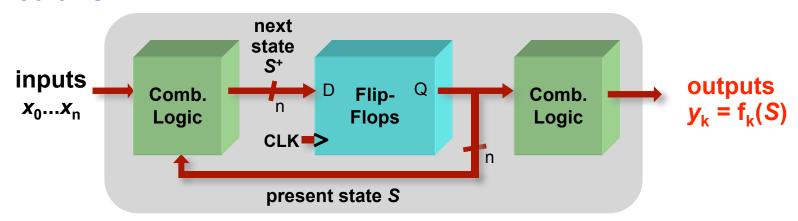

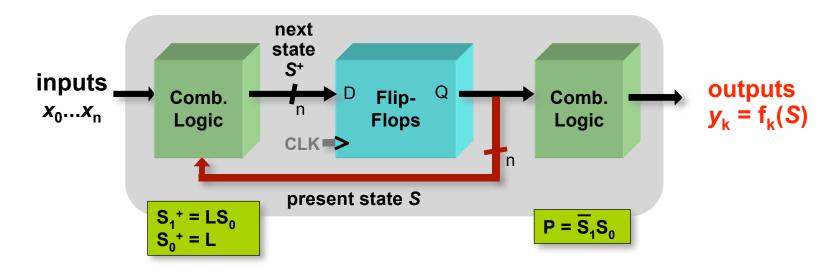

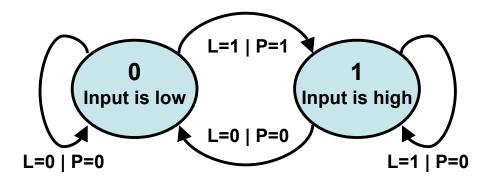

#### III. Finite State Machines

- Finite State Machines (FSMs) are a useful abstraction for sequential circuits with centralized "states" of operation

- At each clock edge, combinational logic computes outputs and next state as a function of inputs and present state

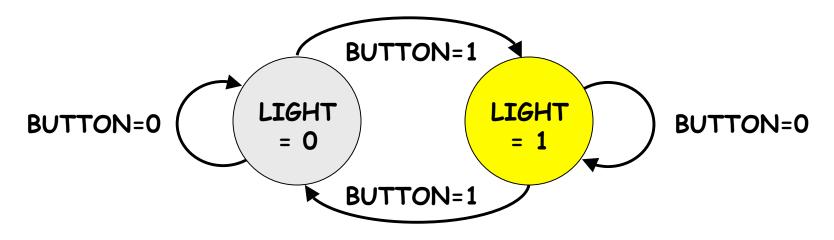

### Example 1: Light Switch

State transition diagram

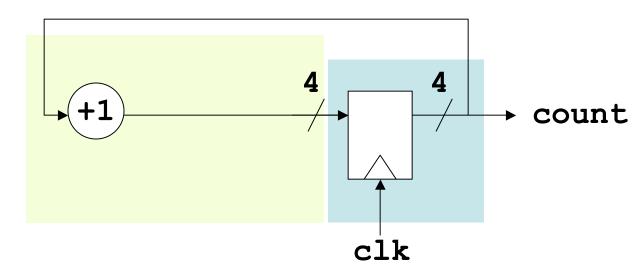

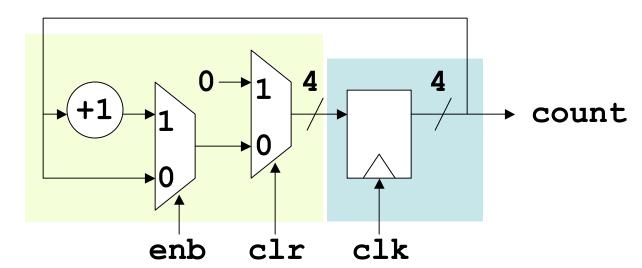

#### Example 2: 4-bit Counter

· Logic diagram

Verilog

```

# 4-bit counter

module counter(clk, count);

input clk;

output [3:0] count;

reg [3:0] count;

always @ (posedge clk) begin

count <= count+1;

end

endmodule</pre>

```

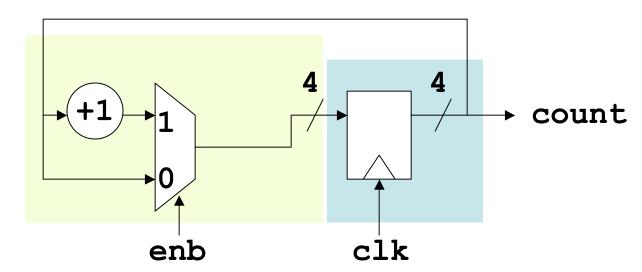

#### Example 2: 4-bit Counter

· Logic diagram

· Verilog

#### Example 2: 4-bit Counter

· Logic diagram

· Verilog

```

# 4-bit counter with enable and synchronous clear

module counter(clk,enb,clr,count);

input clk,enb,clr;

output [3:0] count;

reg [3:0] count;

always @ (posedge clk) begin

count <= clr ? 4'b0 : (enb ? count+1 : count);

end

endmodule</pre>

```

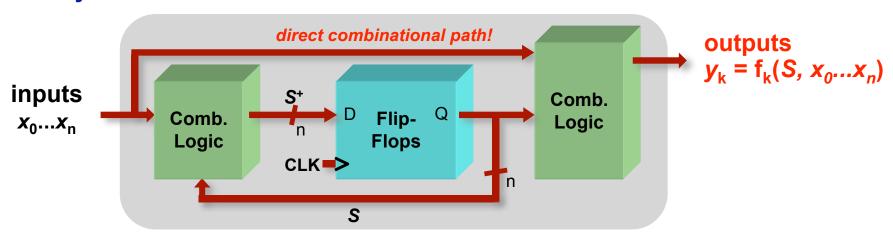

# Two Types of FSMs

Moore and Mealy FSMs: different output generation

#### Moore FSM:

#### Mealy FSM:

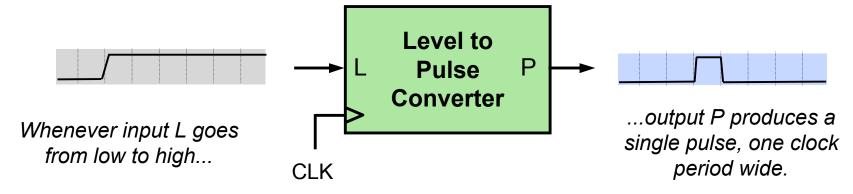

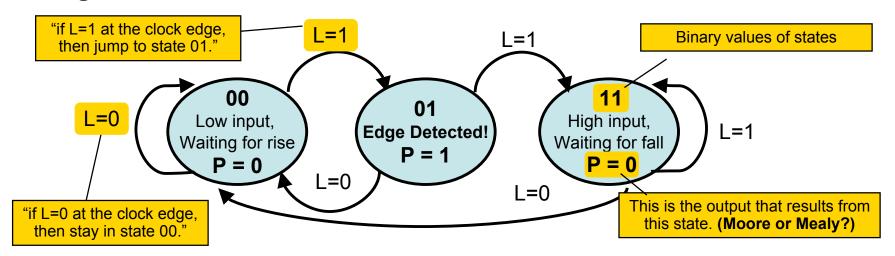

# Design Example: Level-to-Pulse

- A level-to-pulse converter produces a single-cycle pulse each time its input goes high.

- It's a synchronous rising-edge detector.

- Sample uses:

- Buttons and switches pressed by humans for arbitrary periods of time

- Single-cycle enable signals for counters

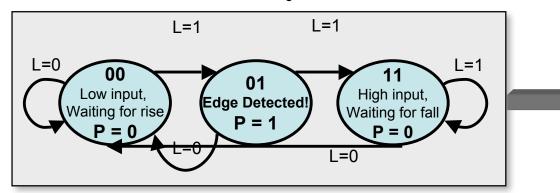

### Step 1: State Transition Diagram

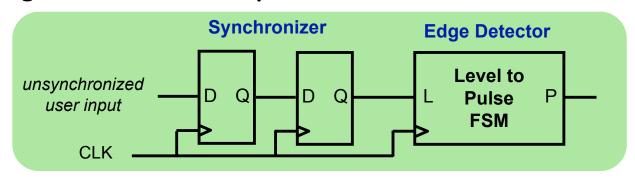

· Block diagram of desired system:

State transition diagram is a useful FSM representation and design aid:

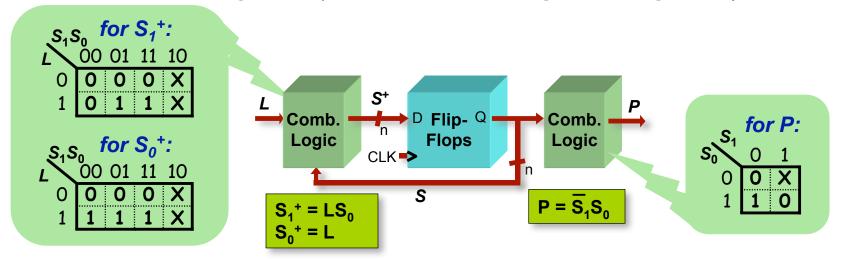

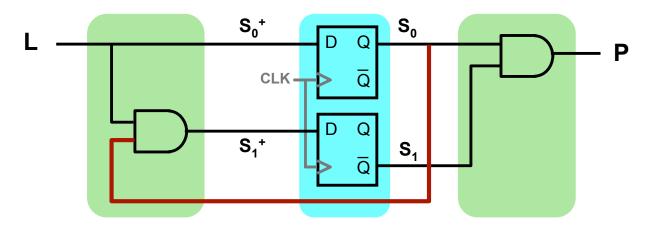

#### Step 2: Logic Derivation

Transition diagram is readily converted to a state transition table (just a truth table)

| Cur<br>t St    | ren<br>tate    | In | Next<br>State    |                                    | Out |

|----------------|----------------|----|------------------|------------------------------------|-----|

| S <sub>1</sub> | S <sub>0</sub> | L  | S <sub>1</sub> + | <b>S</b> <sub>0</sub> <sup>+</sup> | P   |

| 0              | 0              | 0  | 0                | 0                                  | 0   |

| 0              | 0              | 1  | 0                | 1                                  | 0   |

| 0              | 1              | 0  | 0                | 0                                  | 1   |

| 0              | 1              | 1  | 1                | 1                                  | 1   |

| 1              | 1              | 0  | 0                | 0                                  | 0   |

| 1              | 1              | 1  | 1                | 1                                  | 0   |

Combinational logic may be derived using Karnaugh maps

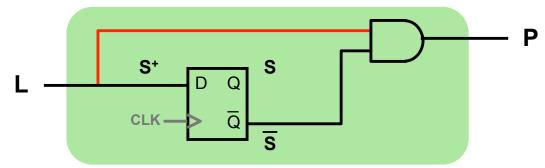

#### Moore Level-to-Pulse Converter

Moore FSM circuit implementation of level-to-pulse converter:

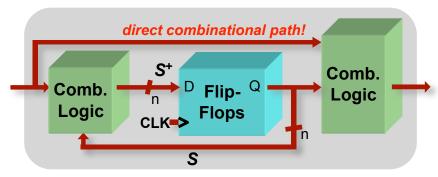

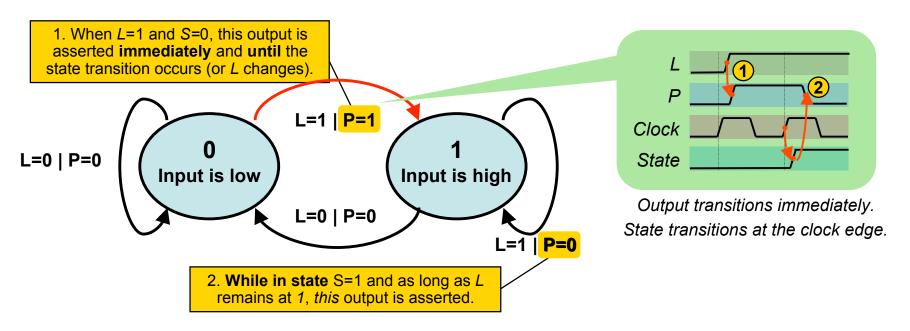

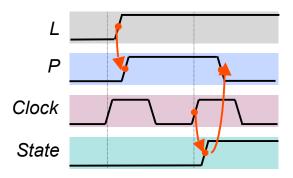

# Design of a Mealy Level-to-Pulse

Since outputs are determined by state and inputs, Mealy FSMs may need fewer states than Moore FSM implementations

### Mealy Level-to-Pulse Converter

| Pres.<br>State | In | Next<br>State  | Out |

|----------------|----|----------------|-----|

| S              | L  | S <sup>+</sup> | P   |

| 0              | 0  | 0              | 0   |

| 0              | 1  | 1              | 1   |

| 1              | 0  | 0              | 0   |

| 1              | 1  | 1              | 0   |

Mealy FSM circuit implementation of level-to-pulse converter:

- FSM's state simply remembers the previous value of L

- Circuit benefits from the Mealy FSM's implicit singlecycle assertion of outputs during state transitions

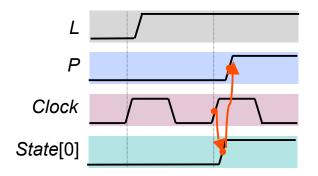

### Moore/Mealy Trade-Offs

- How are they different?

- Moore: outputs = f( state ) only

- Mealy outputs = f( state and input )

- Mealy outputs generally occur one cycle earlier than a Moore:

#### Moore: delayed assertion of P

#### Mealy: immediate assertion of P

- Compared to a Moore FSM, a Mealy FSM might...

- Be more difficult to conceptualize and design

- Have fewer states

# Light Switch Revisited